产品分类

- 财会模拟实验室设备

- 电梯教学设备

- 工程制图实验室设备

- 新能源教学设备

- 化工原理实验装置

- 化工单元操作实训装置

- 化工工程.化工工艺实验装置

- 热工类实验装置

- 环境工程实验装置

- 流体力学实验装置

- 采暖通风实训装置

- 中央空调实训设备

- 制冷制热实训设备

- 煤矿安全技术培训考核设备

- 轨道交通实验实训设备

- 通用电工电子实验室

- 立式电工电子实验台

- 电工.数电.模电.电气控制

- 电机类实验室实训设备

- 电工电子实训考核装置

- 电力电子实验室

- 供配电技术实训设备

- 初.中.高级电工考核柜

- 维修电工实训考核装置

- 电学技术实训与考核设备

- 技师培训实训设备

- 变频调速实验装置

- PLC可编程实训装置

- PLC编程及自动化实验室

- 传感器综合实验台

- 液压实验台

- 气动实验台

- 气动液压综合实验台

- 过程控制工程实验设备

- 电气设备调试与维修实训设备

- 船舶工程技术实训设备

- 机械创新实训台

- 机械示教陈列柜

- 机械仿真设计综合试验装置

- 注塑机演示模型

- 模拟银行实训设备

- 数控机床实训设备

- 数控电气控制与维修实训台

- 机床电气考核设备

- 机床电气实训考核设备(半实物)

- 工业自动化实训设备

- 工业机器人实训设备

- 家电实验室设备

- 计算机原理实验室设备

- 单片机开发综合实验装置

- 机电一体化实训设备

- 钳工实验室设备

- 焊工、铆工实验室成套设备

- 电子工艺实训设备

- 工程机械模拟器

- 工程机械教学实训台

- 农机教学设备

- 智能交通实训设备

- 汽车驾驶模拟器

- 汽车透明教学模型

- 汽车实物解剖模型

- 汽车发动机实训台

- 汽车新能源教学设备

- 汽车程控电教板

- 汽车发动机拆装台架

- 汽车空调系统实验台

- 汽车全车电器实验台

- 汽车发动机翻转架

- 汽车仿真电路实习台

- 汽车变速器实验台

- 汽车底盘实训台

- 汽车ABS.EDS实训台

- 汽车示教板

- 汽车实验箱

- 特殊车辆实训教学设备

- 通用技术实验室设备

- 劳技实验室设备

- 物理实验室成套设备

- 化学实验室成套设备

- 生物实验室成套设备

- 数字化探究实验室设备

- 智能楼宇实训设备

- 心肺复苏模拟人

- 教学模型

- 教学软件

- 教学挂图

- 实验箱

|

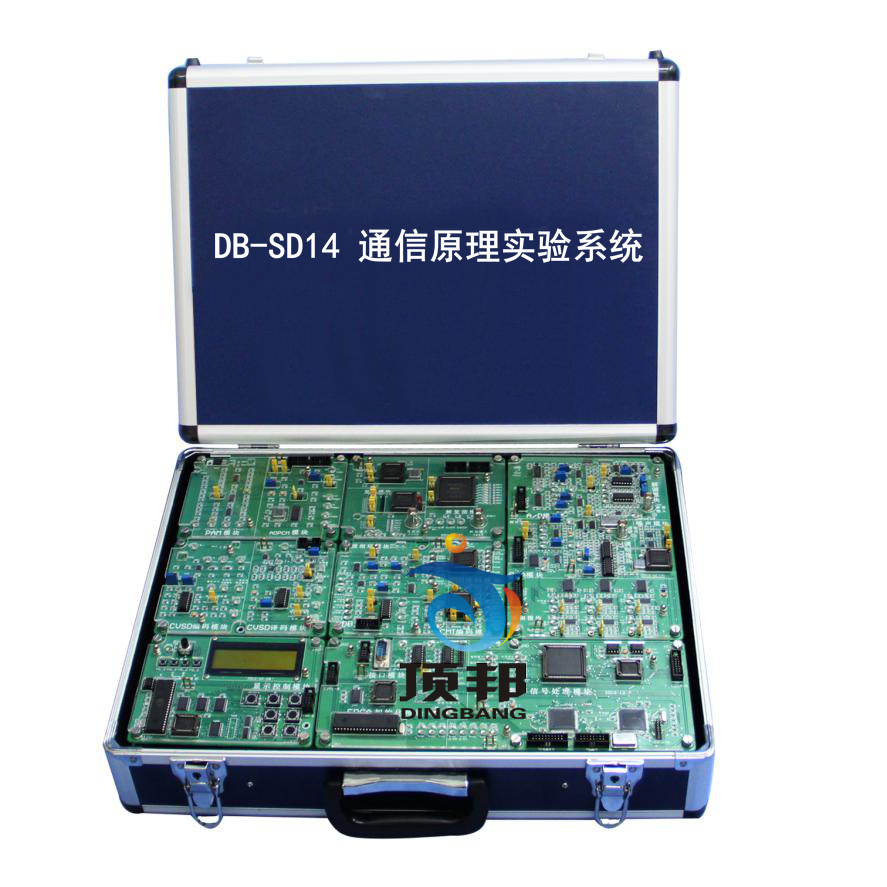

DB-SD14 通信原理实验系统

DB-SD14通信原理实验系统是根据当前各大专院校通信原理课程的教学重点,以现代数字传输技术和软件无线电技术为主要实验方向,强化了有关模拟信号的数字化、各类数字信号的复接与解复接、信源及信道编解码、信息的数字化调制与解调、模拟与数字锁相等内容。为突出重点,集中利用有限的软硬件资源,通过FPGA与DSP的协同工作进行双向信号的编解码处理、信息的数字化调制与解调处理,而舍弃了电话接口电路、电话交换模块等非关键的技术内容。实验中必需的双向信源则采用可任意改变信号频率、信号幅度的内置函数信号发生器以及数字码型发生器代替,通过双踪示波器或误码检测仪等设备观察传输效果。同时,本系统又继承了现代通信技术创新实验系统的模块化设计特点,我公司为其配套的共有9个基本功能模块模块,基本电路设计合理,信源编码包括PAM、ADPAM、PCM、CVSD等,信道编码包括HDB3码、CMI码等;调制解调方式涵盖FSK、BPSK、DBPSK、QPSK、DQPSK、OQPSK、MSK、GMSK、π/4QPSK等;另有模拟调制解调模块(AM、FM)与模拟及数字锁相环等,可配合信号源模块独立地进行相关实验。 本系统的先进设计理念使基本模块可任意拆卸,教师可根据课程需要任意灵活组合电路,构建不同的通信系统。今后还将陆续提供可选扩展模块汉明纠错编解码模块、卷积编解码模块、CDMA原理性扩频解扩模块、OFDM调制解调模块等,使系统功能不断扩展完善。9个功能模块可组成完整的无线通信子系统和有线通信子系统,通过系统实验使学生熟悉现代通信系统的组成,并对通信系统中最新的关键技术有更深的了解。 模块化设计还便于产品维护。设备出现故障或系统升级仅需现场或邮寄更换个别相关模块,一般不会影响系统设备中其它部件的正常使用。 系统多处采用FPGA,FPGA与DSP均预留开放的配置接口,可供师生进行大量的软件二次开发,同时也便于系统升级。因此,系统除了用于通信原理课程的实验,还可以作为一个开放的硬件平台,用于包括FPGA、DSP、单片机编程在内的各类课程设计和毕业设计。 二、电路硬件平台的基本组成 通信原理实验系统由函数信号源模块、PCM/PAM模块、复接/解复接模块、线路编/解码及锁相环模块、CVSD编/解码模块、FPGA与DSP初始化模块、数字信号处理模块、AD/DA与调制/解调模块以及显示控制模块(人机界面)等9个基本功能模块组成,学生通过自行连接信号线贯通各基本模块,构建完整的通信系统,检验和调整各个关键点的信号,可大大加深对现代通信系统概念和结构的理解。 在本系统中,包含两套不对称的传输信道,这样做的目的是为了尽可能多的涵盖通信传输系统各方面的技术: (1)主要体现无线信道传输技术的传输信道,信号流程为:模拟函数信号源→CVSD话音编码(或误码仪的码型信号发生器)→数字调制→信道→数字解调→CVSD话音译码→示波器显示(或误码仪的误码检测器)。 (2)主要体现有线信道传输技术的信号支路,信号流程为:模拟函数信号源→PCM话音编码→信道复接→线路编码(HDB3/CMI)→线路译码→信道解复接→PCM话音译码→示波器显示。 函数信号源模块输出正弦波和方波,TPAO1S、TPAO2S分别为输出端口,VS102调节方波输出大小,调节范围:0~5V。VS103调节正弦波输出大小,调节范围:0~5V;信号输出有高低两个频段:JS01跳线插入、JS02跳线不插输出高频信号,输出信号频率范围20KHz~350KHz;JS01跳线不插、JS02跳线插入,输出低频信号,输出信号频率范围300Hz~2KHz。 三、通信原理实验内容: PAM信源编/译码实验 PCM信源编/译码实验 ADPCM信源编/译码实验 帧成形与帧传输实验 CVSD信源编/译码实验 AMI/HDB3线路码型变换原理实验 HDB3线路编码通信系统综合实验 CMI码型变换原理实验 CMI线路编码通信系统综合实验 汉明纠错编/译码原理实验(正在开发) AM-FM调制/解调原理实验(正在开发) 二进频移键控FSK传输系统调制、解调实验及系统性能测试 二进相移键控BPSK传输系统调制、解调实验及系统性能测试 差分二进制相移键控传输DBPSK系统的调制、解调实验 四相相移键控QPSK传输系统的调制、解调实验 差分四相相移键控DQPSK传输系统的调制、解调实验 四相交错相移键控OQPSK传输系统的调制、解调实验 最小频移键控MSK传输系统的调制、解调实验 高斯最小频移键控传输GMSK系统的调制、解调实验 π/4差分四相相移键控π/4DQPSK传输系统调制、解调实验 模拟锁相环载波同步实验 模拟锁相环时钟提取实验 数字锁相环位同步实验 帧同步提取系统实验 RS422平衡数字传输接口实验 通过FPGA或DSP的预留编程配置接口进行二次开发,内容主要包括: ⑴显示控制模块CPU(89C51系列)键盘扫描程序编制实验 ⑵CPU驱动液晶显示器的应用实验 ⑶显示控制模块中用户操作界面的编程实验 ⑷通过JTAG接口对DSP编程进行DSP信号处理实验 ⑸通过JTAG接口对FPGA编程进行DDS波形生成实验 ⑹通过JTAG接口对FPGA编程实现帧成形实验 ⑺通过JTAG接口对FPGA编程实现帧同步实验 ⑻通过JTAG接口对FPGA、DSP进行综合编程实现AM(有能力还可延伸到QAM、CDMA等)调制/解调实验 友情提示:

1、货品验收:阁下收货时请检查通信原理实验系统的货品外观,核实通信原理实验系统的数量及配件,拒收处于受损状态的通信原理实验系统;

2、质保:顶邦将为阁下提供通信原理实验系统产品说明书内的质保条件和质保期,在质保范围内提供对通信原理实验系统的免费维修,超出条件承诺时提供对通信原理实验系统的有偿维修;

3、退换货:阁下单方面原因导致的通信原理实验系统选型错误或通信原理实验系统购买数量错误,造成通信原理实验系统的退换货要求,将不被接受;

4、货期:通信原理实验系统的发货期为参考值,如您需要了解通信原理实验系统的精确货期,请与顶邦的销售人员联系;

5、如阁下对通信原理实验系统有任何疑问,请致电:021-36334717 ,我们将由专业人士为您提供有关通信原理实验系统的咨询。

|

| 相关产品 |

| 模拟电路实验箱 |

| 交流电路实验箱 |

| 光纤通信实验箱 |

| 相控整流电路实验箱 |

| 高频实验箱 |

| AI语音与机器视觉开发应用系统平台 |

| 嵌入式边缘物联网实验平台 |

| EDA设计技术实验箱 |

| 自控原理与计算机控制实验仪 |

| 8-32位微机原理接口实验系统 |

| 信号与系统实验平台 |

| EDA技术实验系统 |

| 多功能单片机实验开发系统 |

| 信号与系统及数字信号处理平台 |

| 计算机组成原理与系统结构实验箱 |

| 微波射频与天线实验箱 |

| 嵌入式ARM实验箱 |

| Android 3G智能手机开发实训平台 |

| 电工技术实验箱 |

| 现代单片机.微机.EDA综合实验开发系统 |